# Epson / E Ink EPD Controller

# S4E5B001B000A00 EPD Controller Module

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2012 - 2013, All rights reserved.

# **Table Of Contents**

| Chapter | 1 Introduction                                                               |

|---------|------------------------------------------------------------------------------|

| 1.1     | Scope                                                                        |

| 1.2     | Overview Description                                                         |

| Chapter | 2 Features                                                                   |

| 2.1     | Direct Source and Gate Driver for Electrophoretic Display                    |

| 2.2     | 8/16-Bit and Serial Host Interface                                           |

| 2.3     | Advanced Sequencer Engine                                                    |

| 2.4     | Memory                                                                       |

| 2.5     | Image Buffer Flexibility                                                     |

| 2.6     | Picture-In-Picture                                                           |

| 2.7     | Cursor Buffer Support                                                        |

| 2.8     | Thermal Sensor                                                               |

| 2.9     | Four Regulated Output Voltages for Source- and Gate-Driver Power Supplies 10 |

| 2.10    | VCOM Power Supply                                                            |

| 2.11    | Controlled Inrush Current During Soft Start                                  |

| 2.12    | Clock Source                                                                 |

| Chapter | 3 Typical System Implementation                                              |

| Chapter | 4 Pins                                                                       |

| 4.1     | Pinout Diagram                                                               |

| 4.2     | Pin Descriptions                                                             |

| 4       | .2.1 Shared Host Interface                                                   |

| 4       | .2.2 Host Interface                                                          |

| 4       | .2.3 Gate Driver Interface                                                   |

| 4       | .2.4 Source Driver Interface                                                 |

| 4       | .2.5 Miscellaneous                                                           |

| 4       | .2.6 Power and Ground                                                        |

| 4.3     | Configuration Pins                                                           |

| 4.4     | Pin Mapping                                                                  |

| 4       | .4.1 Host Interface Modes                                                    |

| Chapter | 5 D.C. Characteristics                                                       |

| 5.1     | Absolute Maximum Ratings                                                     |

| 5.2     | Recommended Operating Conditions                                             |

| 5.3     | Electrical Characteristics                                                   |

| Chapter | 6 A.C. Timings                                                               |

| 6.1     | Power-On Sequence                                                            |

| 6.2     | RESET_L Timing                                                               |

| 6.3       | Host Interface Timing                                   |  |

|-----------|---------------------------------------------------------|--|

| 6.        | 3.1 Intel 80 Host Interface Timing                      |  |

| 6.        | 3.2 Serial Host Interface Timing                        |  |

| Chapter 3 | 7 Power Management                                      |  |

| 7.1       | Power Management State Description                      |  |

| Chapter a | 8 Host Interface                                        |  |

| 8.1       | Host Cycle Sequences                                    |  |

| 8.        | 1.1 Command and Parameter Cycle                         |  |

| 8.        | 1.2 Memory Access Combination Cycle                     |  |

| 8.2       | HRDY (Wait Line) Usage                                  |  |

| 8.3       | Intel 80 16-Bit Host Operations                         |  |

| 8.4       | Intel 80 8-Bit Host Operations                          |  |

| 8.5       | Serial Host Operations                                  |  |

| 8.:       | 5.1 Protocol Timing                                     |  |

| 8.:       | 5.2 Command Transfers                                   |  |

| 8.6       | Command List                                            |  |

| 8.7       | Host Interface Command Descriptions                     |  |

| 8.2       | 7.1 INIT_PLL $(0x01 + 3 \text{ parameters})$            |  |

| 8.2       | 7.2 RUN_SYS $(0x02 + 0 \text{ parameters}) \dots \dots$ |  |

| 8.′       | 7.3 STBY $(0x04 + 0 \text{ parameters})$                |  |

| 8.2       | 7.4 SLP $(0x05 + 0 \text{ parameters})$                 |  |

| 8.2       | 7.5 INIT_SYS_RUN $(0x06 + 0 \text{ parameters})$        |  |

| 8.′       | 7.6 INIT_ROTMODE $(0x0B + 1 \text{ parameter})$         |  |

| 8.2       | 7.7 RD_REG $(0x10 + 2 \text{ parameters})$              |  |

| 8.2       | 7.8 WR_REG $(0x11 + 2 \text{ parameters})$              |  |

| 8.2       | 7.9 PIP_DISABLE $(0x14 + 0 \text{ parameters})$         |  |

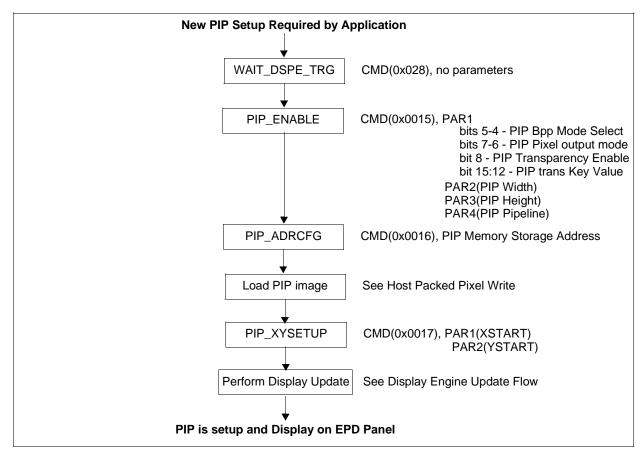

| 8.2       | 7.10 PIP_ENABLE $(0x15 + 4 \text{ parameters}) \dots$   |  |

| 8.2       | 7.11 PIP_ADRCFG $(0x16 + 2 \text{ parameters}) \dots$   |  |

| 8.2       | 7.12 PIP_XYSETUP $(0x17 + 2 \text{ parameters})$        |  |

|           | 7.13 CSR_MAINCFG $(0x18 + 4 \text{ parameter})$         |  |

| 8.2       | 7.14 CSR_XYSETUP $(0x19 + 2 \text{ parameters})$        |  |

| 8.2       | 7.15 CSR_ADRCFG $(0x1A + 1 \text{ parameters})$         |  |

| 8.7       | 7.16 BST_RD_SDR $(0x1C + 4 \text{ parameters})$         |  |

| 8.7       | 7.17 BST_WR_SDR $(0x1D + 4 \text{ parameters})$         |  |

| 8.2       | 7.18 BST_END_SDR $(0x1E + 0 \text{ parameters})$        |  |

| 8.7       | 7.19 LD_IMG $(0x20 + 1 \text{ parameter})$              |  |

| 8.2       | 7.20 LD_IMG_AREA $(0x22 + 5 \text{ parameters})$        |  |

|           | 7.21 LD_IMG_END $(0x23 + 0 \text{ parameters})$         |  |

| 8.        | 7.22 LD_IMG_SETADR (0x25 + 2 parameters).               |  |

| 8.7.23 LD_IMG_DSPEADR $(0x26 + 0 \text{ parameters})$                                                        | 60 |

|--------------------------------------------------------------------------------------------------------------|----|

| 8.7.24 WAIT_DSPE_TRG (0x28 + 0 parameters)                                                                   | 60 |

| 8.7.25 WAIT_DSPE_FREND (0x29 + 0 parameters)                                                                 | 60 |

| 8.7.26 WAIT_DSPE_LUTFREE (0x2A + 0 parameters)                                                               | 60 |

| 8.7.27 RD_WFM_INFO (0x30 + 2 parameters)                                                                     | 61 |

| 8.7.28 UPD_INIT $(0x32 + 0 \text{ parameters})$                                                              | 61 |

| 8.7.29 UPD_FULL (0x33 + 1 parameter)                                                                         | 62 |

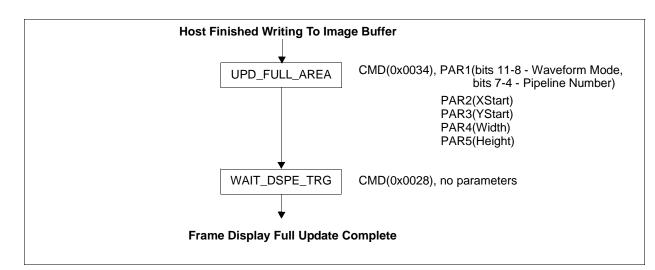

| 8.7.30 UPD_FULL_AREA (0x34 + 5 parameters)                                                                   | 62 |

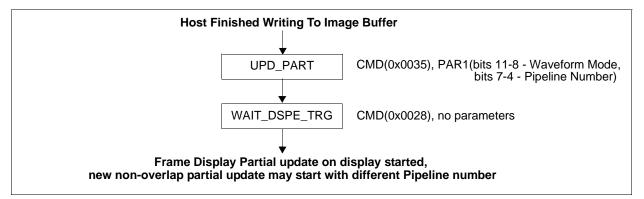

| 8.7.31 UPD_PART (0x35 + 1 parameter)                                                                         | 64 |

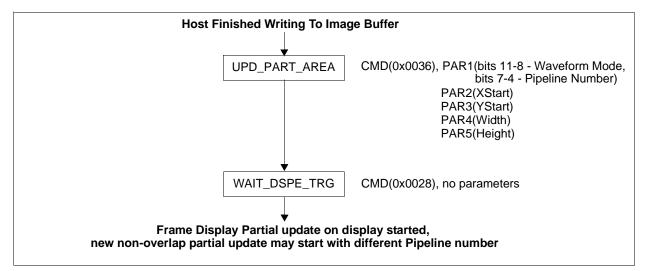

| 8.7.32 UPD_PART_AREA (0x36 + 5 parameters)                                                                   | 65 |

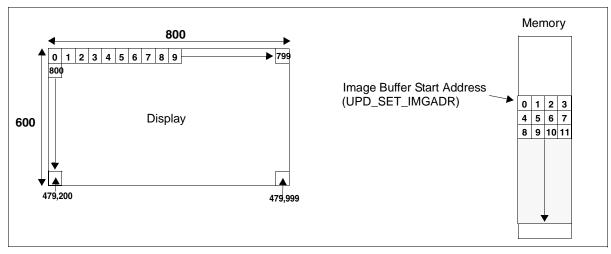

| 8.7.33 UPD_SET_IMGADR (0x38 + 2 parameters)                                                                  | 67 |

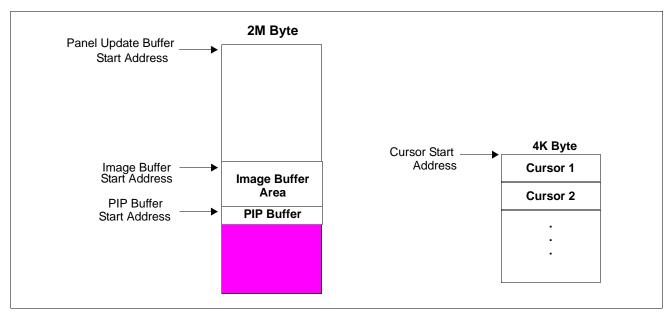

| Chapter 9 Display Memory Configurations                                                                      | 68 |

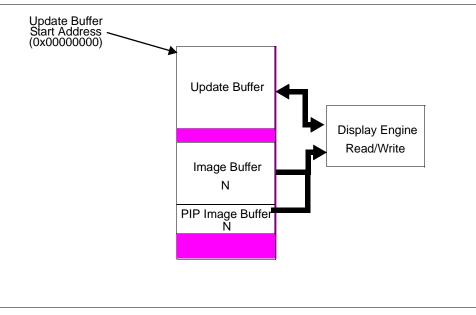

| 9.1 Introduction                                                                                             | 68 |

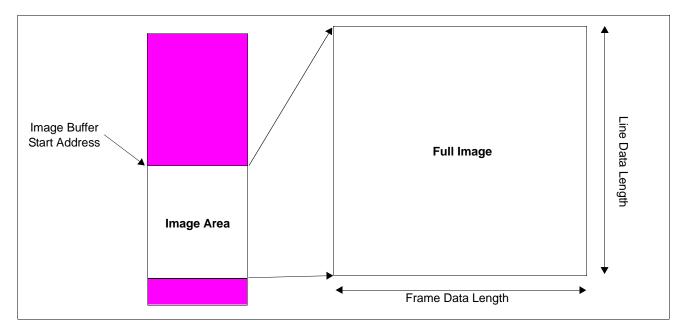

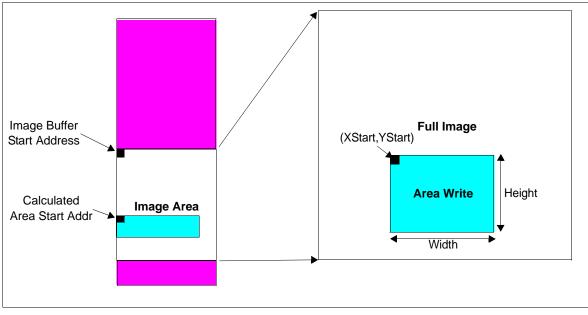

| 9.2 Image Buffer Memory Area Setup                                                                           | 69 |

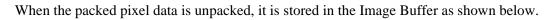

| 9.2.1 Image Buffer Storage                                                                                   | 70 |

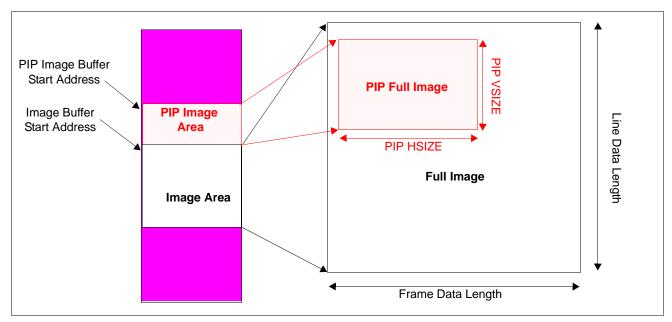

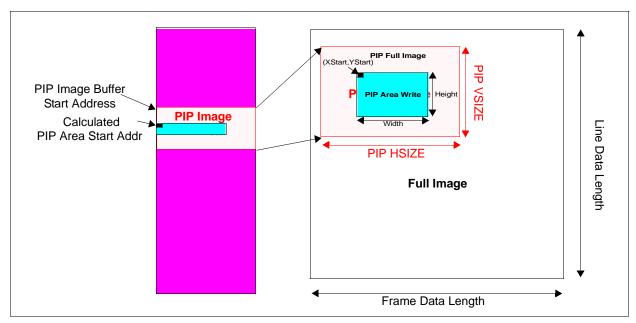

| 9.3 PIP Image Buffer Memory Area Setup                                                                       | 71 |

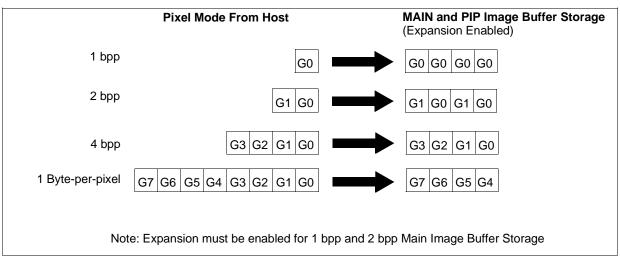

| 9.3.1 PIP Image Buffer Storage                                                                               | 72 |

| 9.4 Panel Update Buffer Memory Area Setup                                                                    | 72 |

| 9.4.1 Panel Update Buffer Usage                                                                              | 73 |

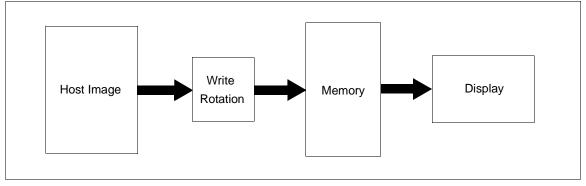

| 9.5 Rotation Support                                                                                         | 74 |

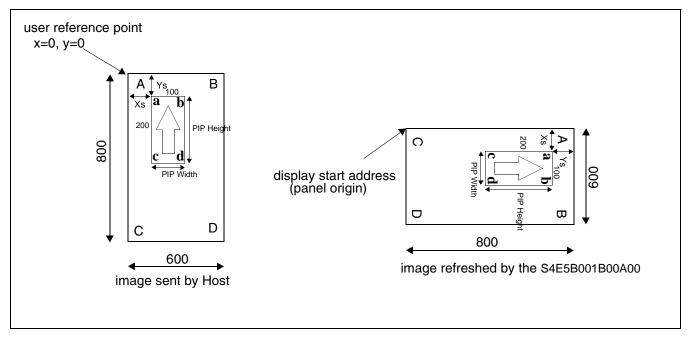

| 9.5.1 Rotation Introduction                                                                                  | 74 |

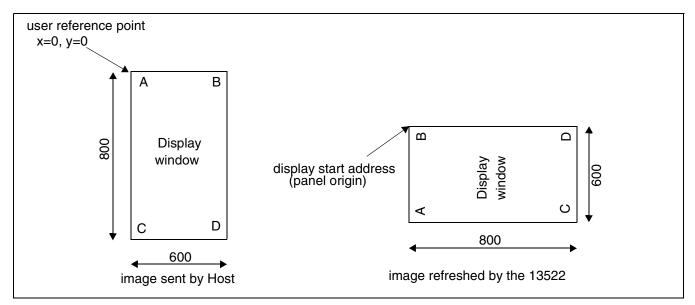

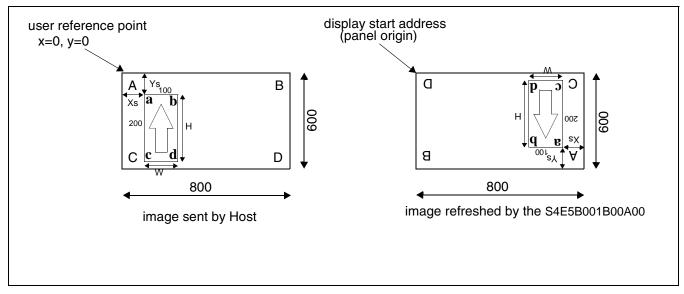

| 9.5.2 90° Rotation $\ldots$ | 75 |

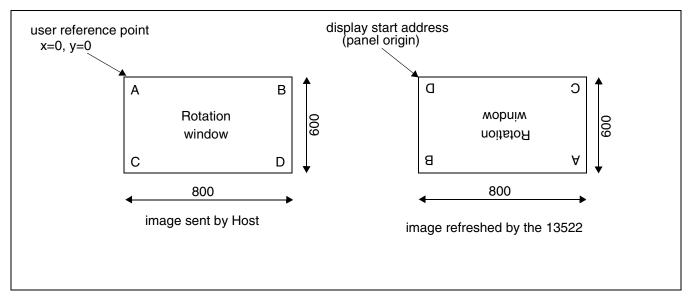

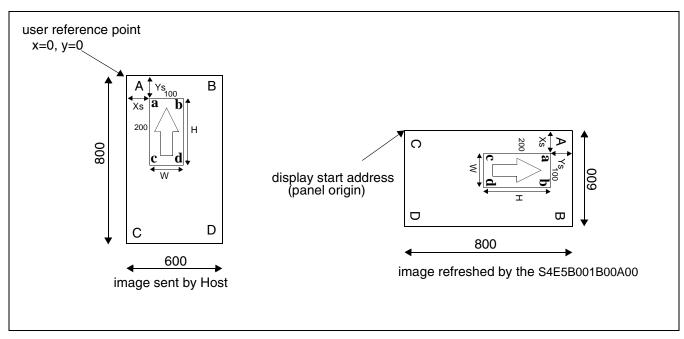

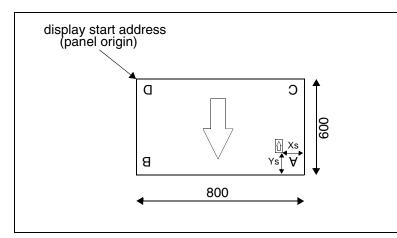

| 9.5.3 180° Rotation                                                                                          | 76 |

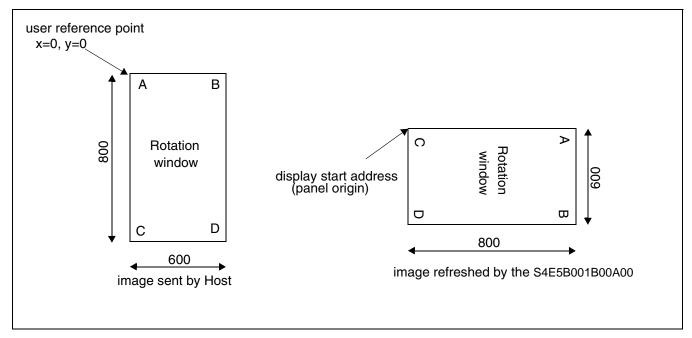

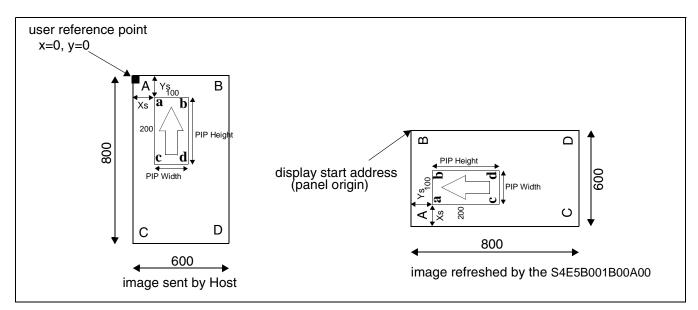

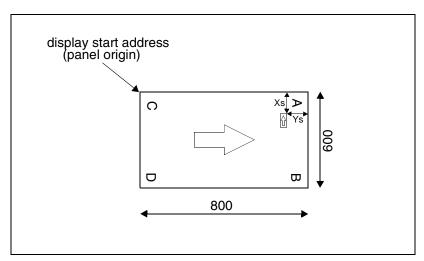

| 9.5.4 270° Rotation                                                                                          | 77 |

| 9.6 Window Area Position / Rotation                                                                          | 78 |

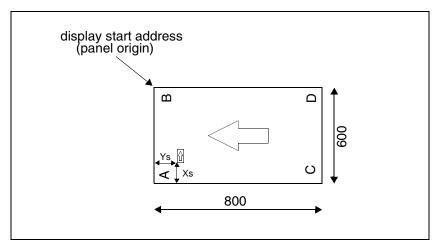

| 9.6.1 90° Rotation                                                                                           | 78 |

| 9.6.2 180° Rotation                                                                                          | 79 |

| 9.6.3 270° Rotation                                                                                          | 80 |

| 9.7 PIP Relative to Panel Rotation                                                                           | 81 |

| 9.7.1 90° Rotation                                                                                           | 81 |

| 9.7.2 180° Rotation                                                                                          | 82 |

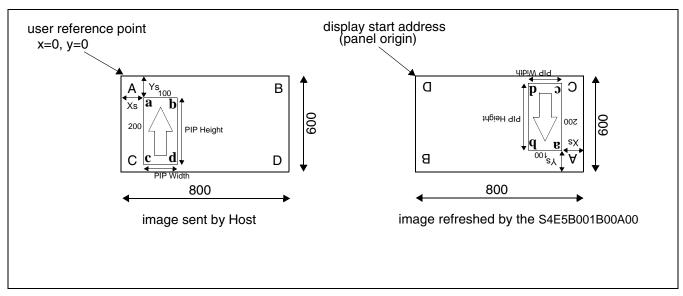

| 9.7.3 270° Rotation                                                                                          | 83 |

| 9.8 Cursor Relative to Panel Rotation                                                                        | 84 |

| 9.8.1 90° Rotation                                                                                           | 84 |

| 9.8.2 180° Rotation                                                                                          | 85 |

| 9.8.3 270° Rotation                                                                                          | 86 |

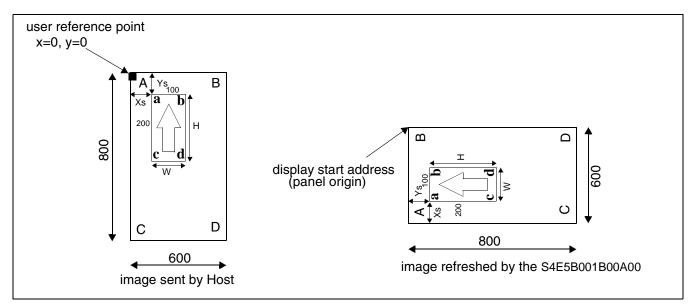

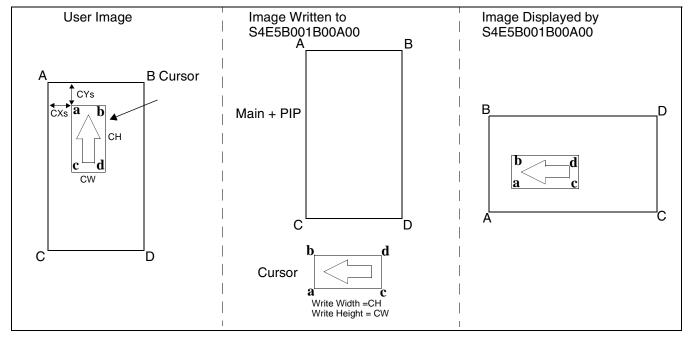

| 9.8.4 Cursor Rotation Example                                                                                | 87 |

| Chapter 10 Host Memory Transfer Format                                                                       | 88 |

| 10.1 Host Interface Memory Transfer Mode                                                                     | 88 |

| 10.2 Host Interface Packed Pixel Data Transfer Format Endian Formatting   |

|---------------------------------------------------------------------------|

| 10.2.1 Packed Pixel Area Size Transfer Example                            |

| Chapter 11 Display Operations                                             |

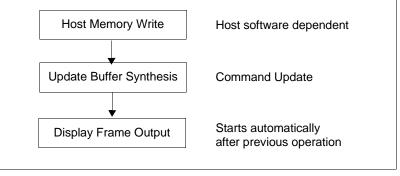

| 11.1 Display Update: Multi-Region Pipeline Usage                          |

| 11.1.1 User Interface Applications with Multi-Region Pipeline             |

| 11.1.2 Display Update Commands                                            |

| 11.1.3 Pipeline Usage                                                     |

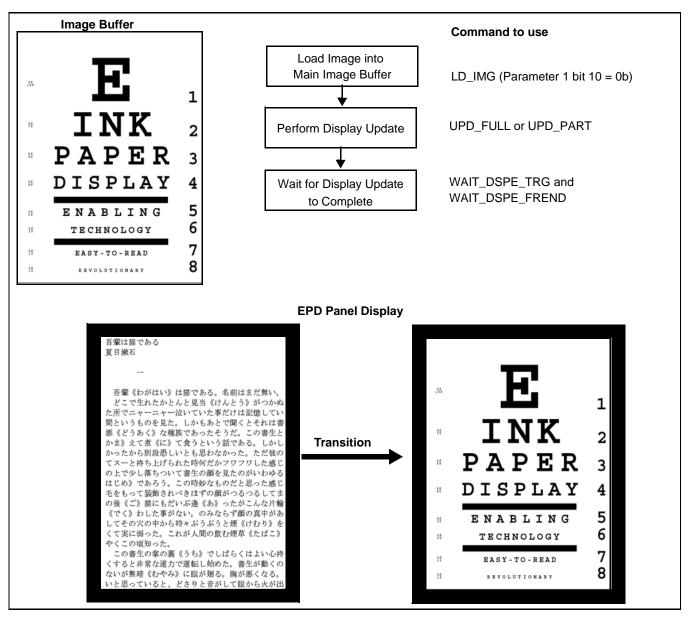

| 11.2 Guaranteed Display Update Operation Flow                             |

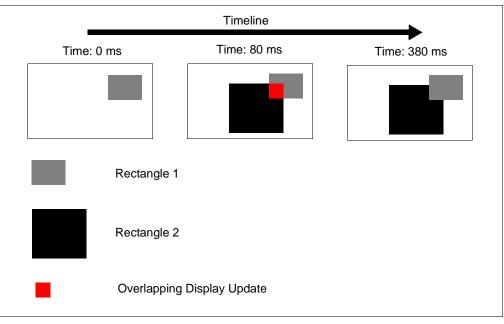

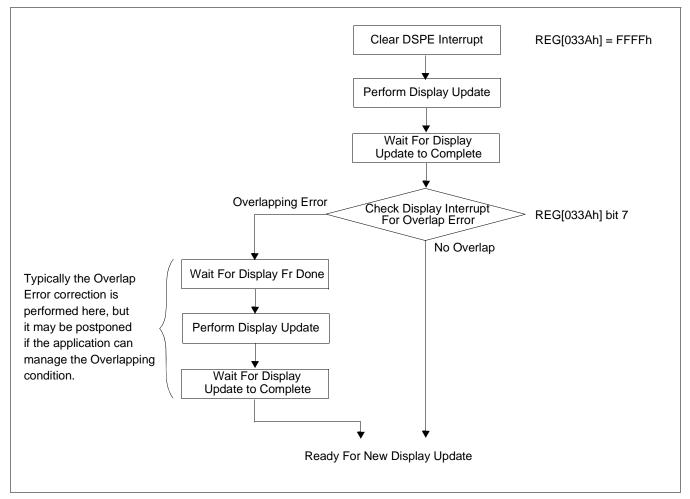

| 11.3 Overlapping Display Update Operation Flow                            |

| 11.3.1 Overlapping Display Updates                                        |

| 11.3.2 Overlapping Display Update Recommended Programming Flow            |

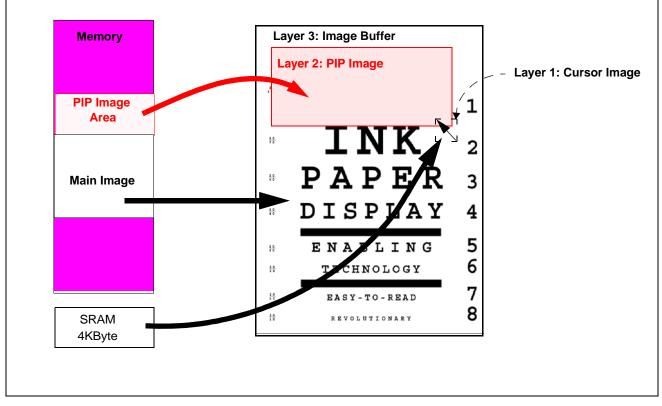

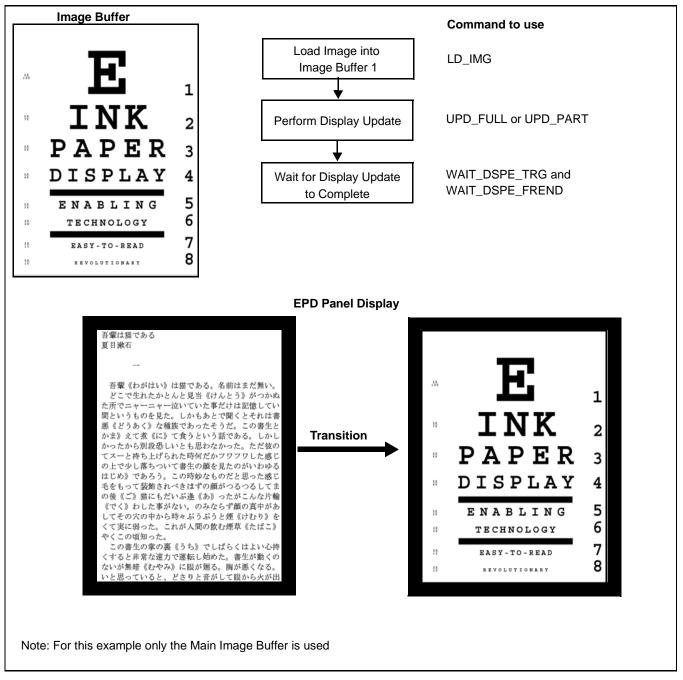

| 11.4 Multi-layer Image Buffer Support                                     |

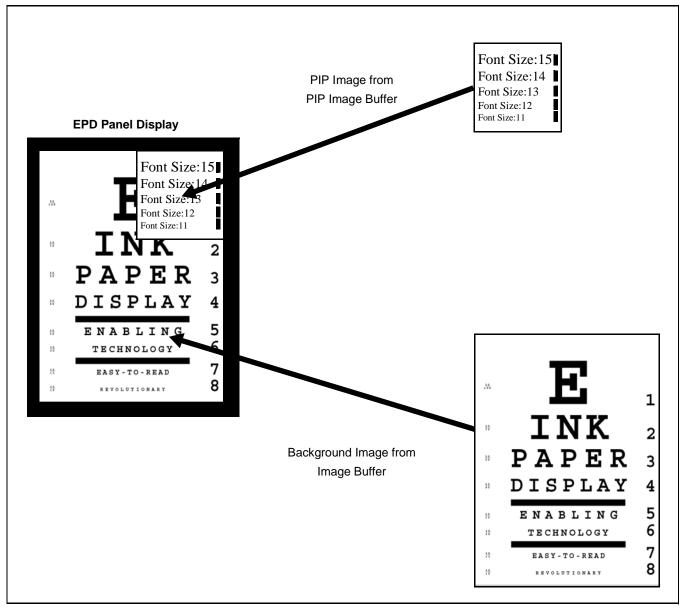

| 11.5 PIP Window Support                                                   |

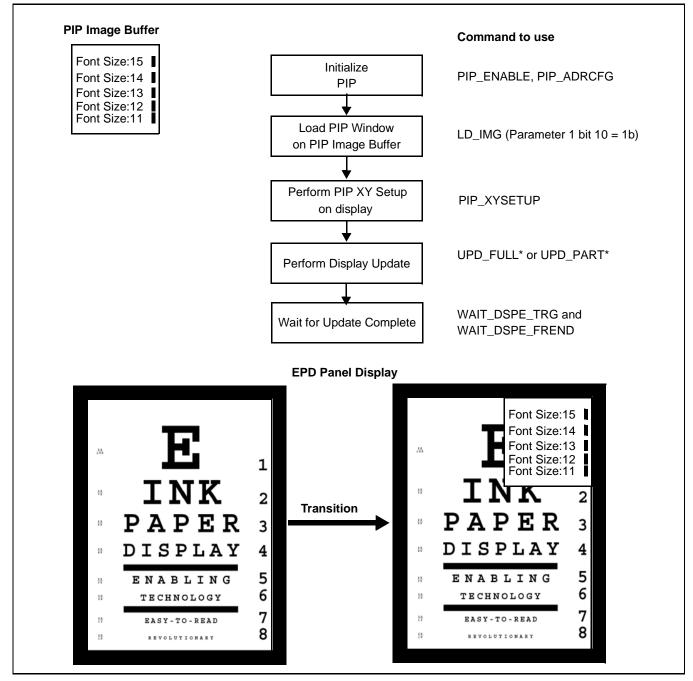

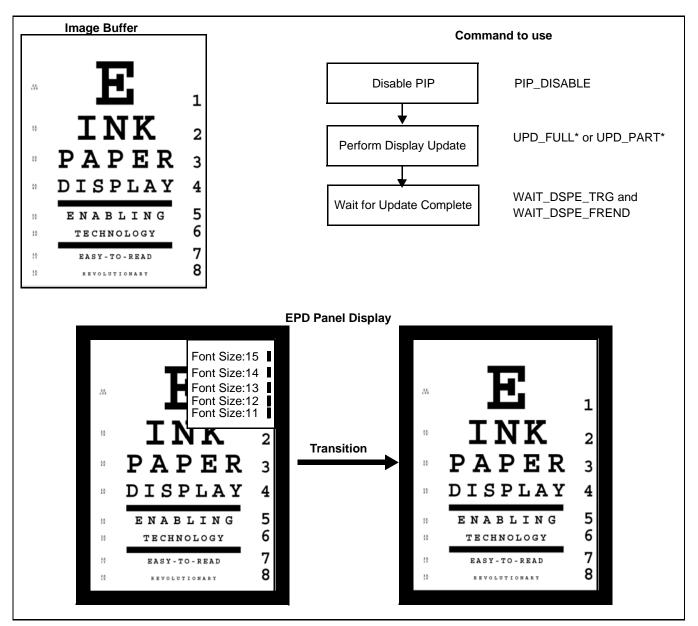

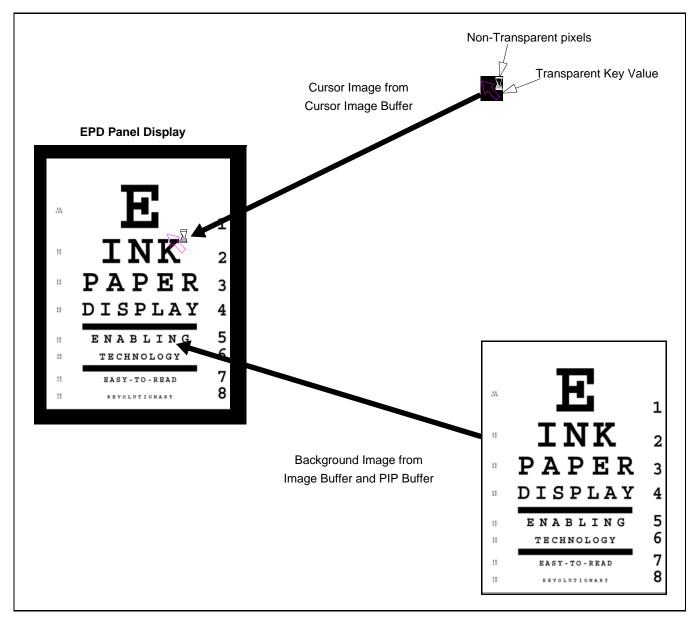

| 11.5.1 PIP Window Implementation                                          |

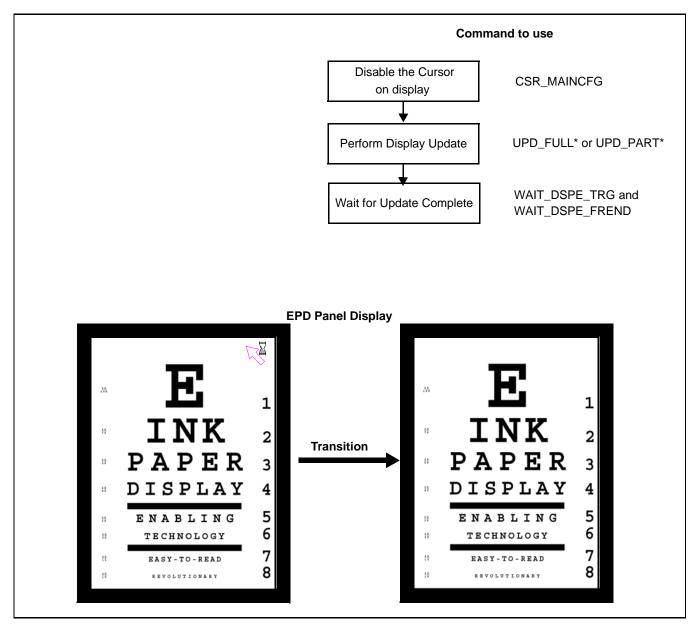

| 11.6 Cursor Window Support                                                |

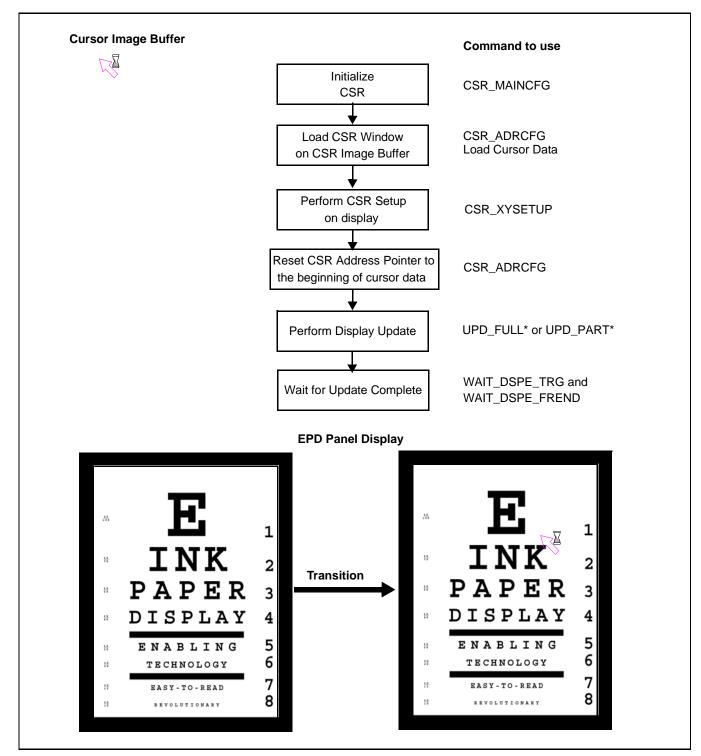

| 11.6.1 Cursor Window Implementation                                       |

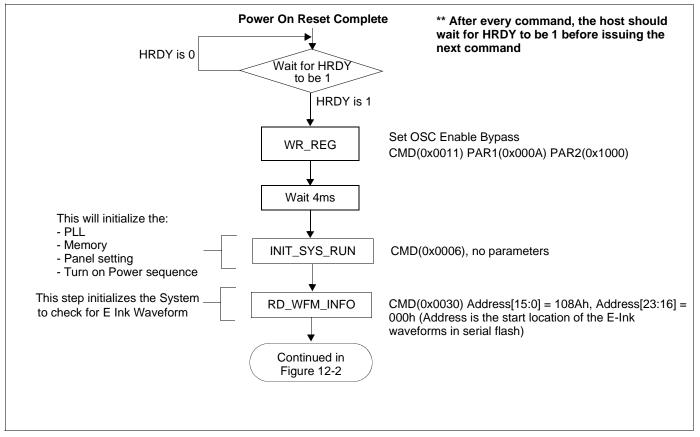

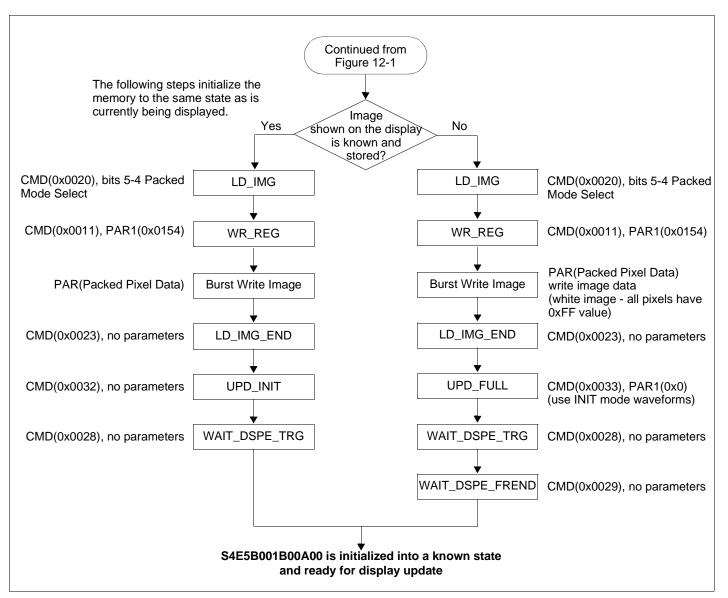

| Chapter 12 Firmware Programming Guide                                     |

| 12.1 Command Based Programming                                            |

| 12.1.1 Power On Initialize                                                |

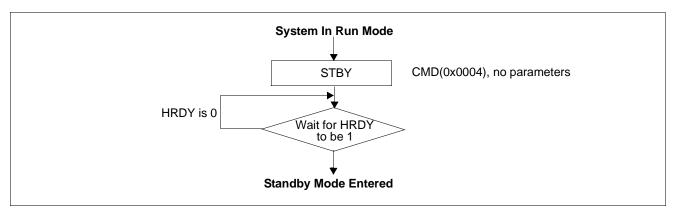

| 12.1.2 Standby Mode                                                       |

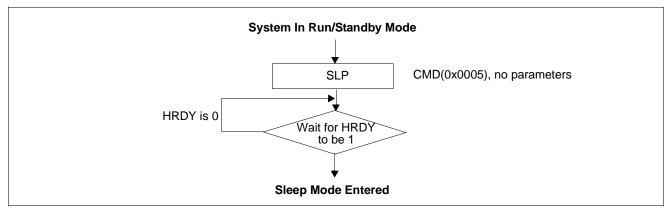

| 12.1.3 Sleep Mode                                                         |

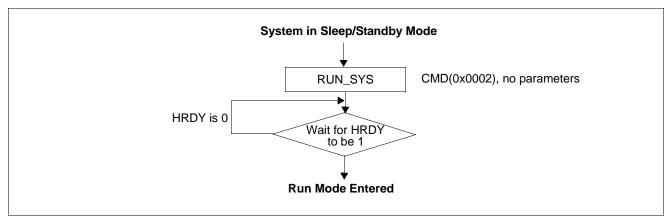

| 12.1.4 Run Mode                                                           |

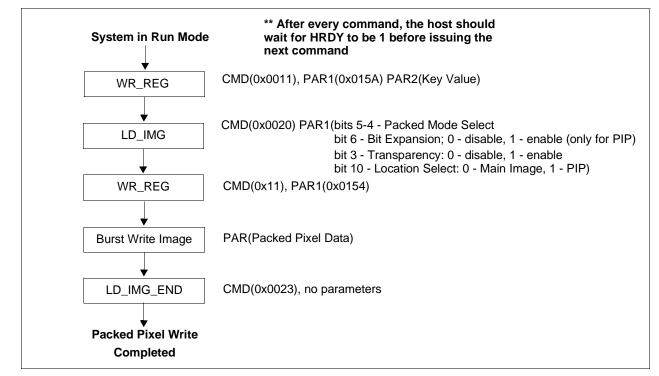

| 12.1.5 Host Packed Pixel Write - to Main or PIP with Transparency         |

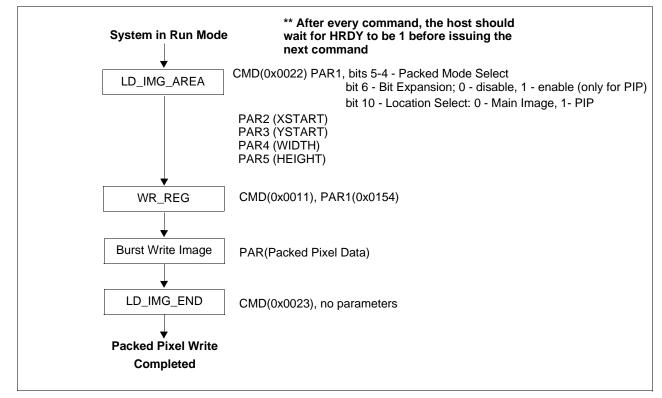

| 12.1.6 Host Area Defined Packed Pixel Write - to Main or PIP              |

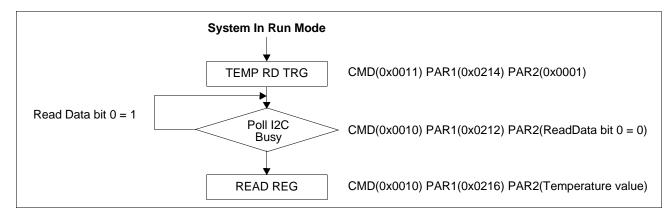

| 12.1.7 Manual Trigger to Thermal Sensor for Single Temperature Read       |

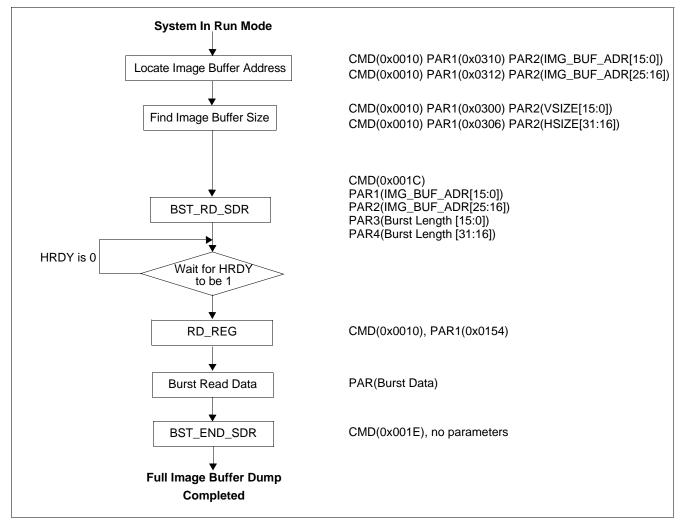

| 12.1.8 Full Image Buffer Dump                                             |

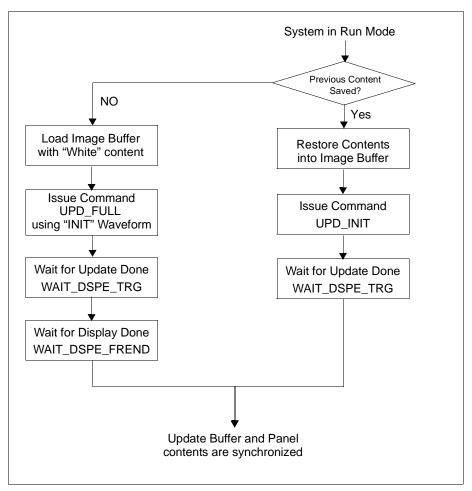

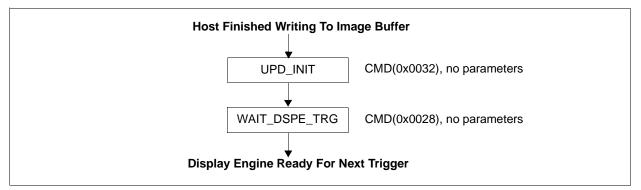

| 12.1.9 Display Engine - Panel Update Buffer Initialize with Image Buffer  |

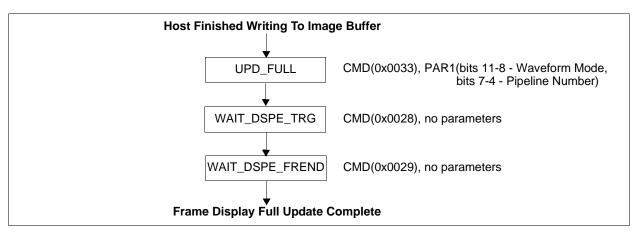

| 12.1.10 Display Engine - Full Display Update - Full Image Size Sweep      |

| 12.1.11 Display Engine - Full Display Update - User Defined Area Sweep    |

| 12.1.12 Display Engine - Partial Display Update - Full Image Size Sweep   |

| 12.1.13 Display Engine - Partial Display Update - User Defined Area Sweep |

| 12.1.14 Display Engine - Picture-In-Picture Setup                         |

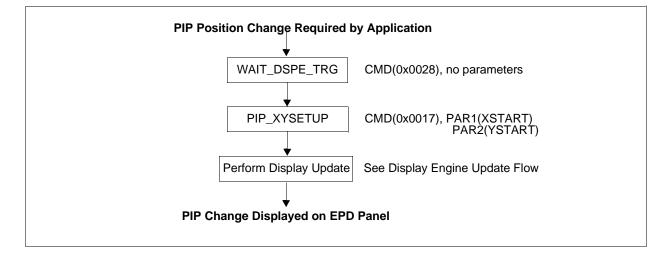

| 12.1.15 Display Engine - Picture-In-Picture Position Change               |

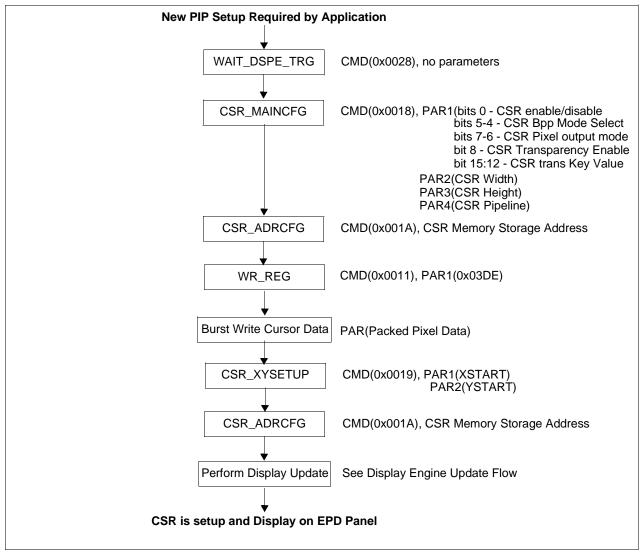

| 12.1.16 Display Engine - Cursor Setup                                     |

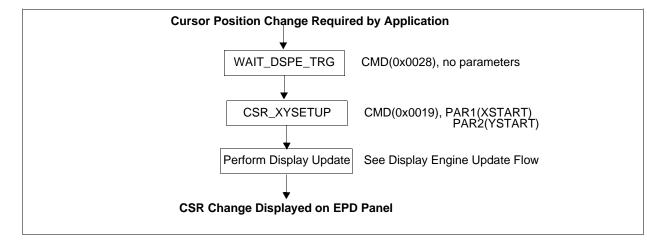

| 12.1.17 Display Engine - Cursor Position Change                           |

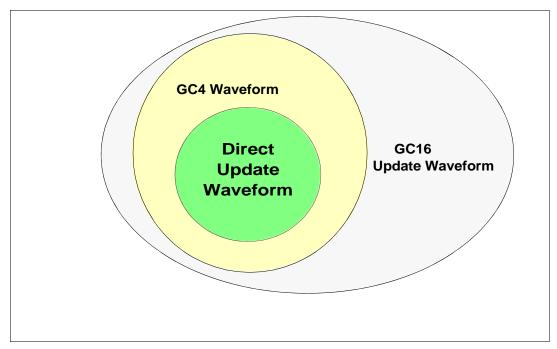

| Chapter 13 Auto Waveform                                                  |

| 13.1 Introduction                                                         |

| 13.2 Waveform Modes                                                       |

| Chapter 14 Timing Requirements                                            |

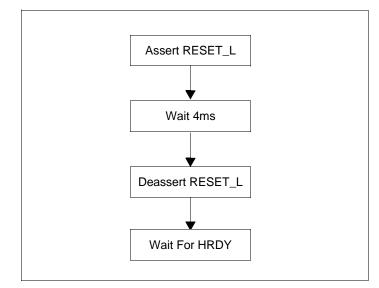

| 14.1 Timing Requirements For Reset    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

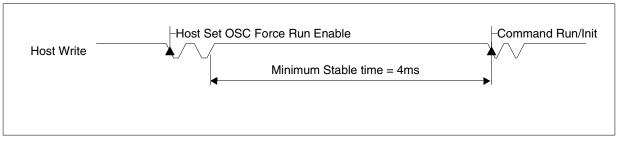

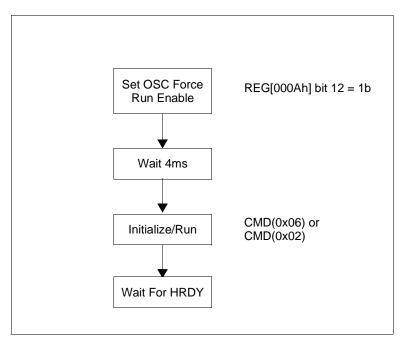

| 14.2 Timing Requirements for Initialization or Exiting from Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

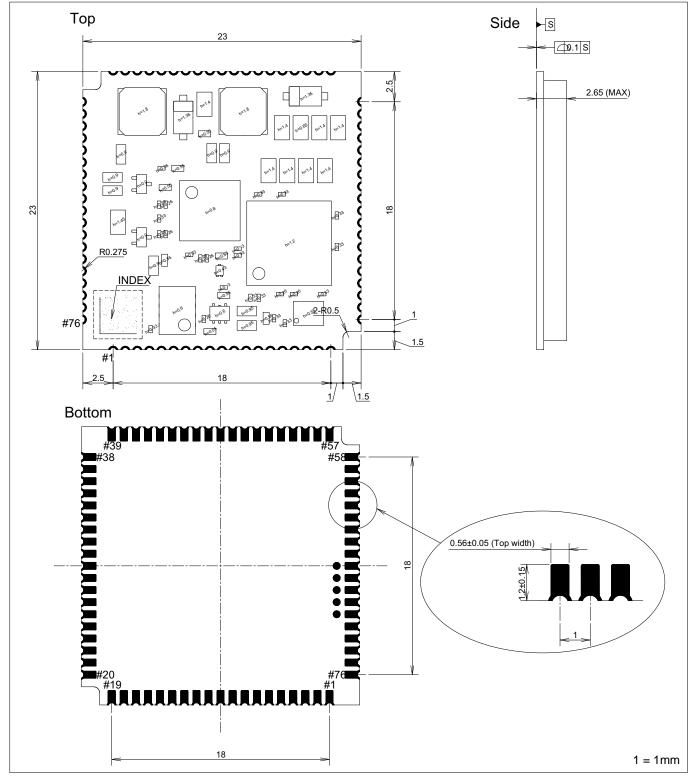

| Chapter 15 Mechanical Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Chapter 16 Soldering, Handling and Storage Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

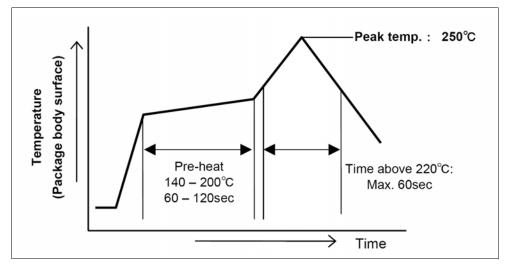

| 16.1 Recommended Reflow Profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 16.1.1 Repeat Reflow Soldering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| 16.1.2 Baking Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| 16.1.3 Hand Soldering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 16.1.4 Pb-Free Soldering Paste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| 16.1.5 Cleaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 16.1.6 Visual Inspection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| 16.1.7 Rework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| 16.2 Handling and Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| 16.2.1 Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 16.2.2 Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Chapter 17 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| Appendix A Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| A.1 Register Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| A.1.1 Register Access using Command Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| A.2 Register Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| A.3 Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

# Chapter 1 Introduction

## 1.1 Scope

This is the Hardware Functional Specification for the S4E5B001B00A00 EPD Controller Module. Included in this document are timing diagrams, AC and DC characteristics, Command descriptions, and power management descriptions. This document is intended for initial system designer references only.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. We appreciate your comments on our documentation. Please contact us via email at documentation@erd.epson.com.

## **1.2 Overview Description**

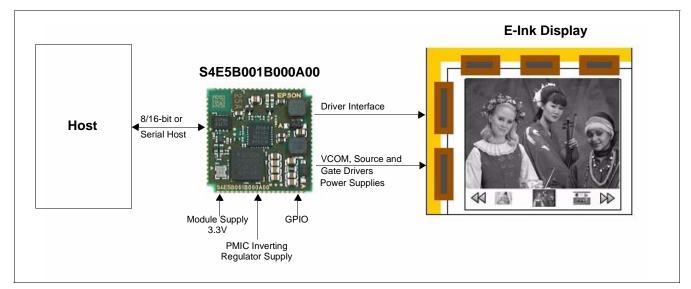

EPSON's S4E5B001B000A00 EPD Controller Module is a complete, high performance, easy to use solution for E Ink EPDs (Electronic Paper Displays). The module includes all necessary digital and analog power circuitry for driving an E Ink panel. The EPD Controller Module consists of Epson's S1D13522 EPD controller, an on-board 26MHz crystal clock source, an 8 Mbit flash memory for command/waveform storage, and a Power Management IC (PMIC) with built in temperature sensor.

The S4E5B001B000A00 EPD Controller Module contains all the complex electronics needed to drive an EPD panel. With this module a customer can build a EPD system on a simple two layer PCB. This module removes the complexity of board design from the customer, making a variety of implementations possible.

The S4E5B001B000A00 EPD Controller Module is the ideal choice for new EPD designs and design upgrades.

Figure 1-1: S4E5B001B00A00 Overview

## **Chapter 2 Features**

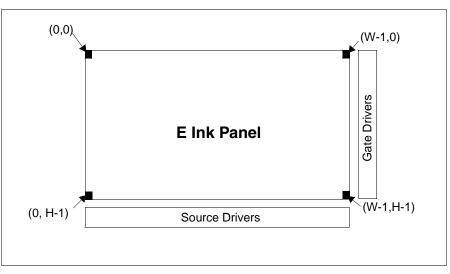

#### 2.1 Direct Source and Gate Driver for Electrophoretic Display

- Up to 4-bit grayscale waveforms (16 level grey-shades)

- Source Driver interfaces to the Micronix MX860 IC and compatible devices

- Gate Driver interfaces to the Sharp LH1692 and compatible devices

- 15-Region Pipeline Technology

- Auto Pipeline Management for easy implementation

- Auto Waveform Management

- Automatically determines the best/fastest waveforms based on the display contents

- Supports Monochrome, 4 level grayscale, 8 level grayscale, 16 level grayscale and one default waveform

#### 2.2 8/16-Bit and Serial Host Interface

- Indirect 8/16-bit Host Bus Interface (Intel 80)

- Serial Host Interface (SPI)

- Registers can be accessed using Command Mode

- DMA compatible memory bus style host interface

- Transparency write support

### 2.3 Advanced Sequencer Engine

• Sequencer logic executes pre-programmed series of commands request from host.

#### 2.4 Memory

- 2M Bytes of stacked memory

- Sufficient Storage for:

|                                                             |              | Panel Size    | Memory Storage Configuration            |                              |

|-------------------------------------------------------------|--------------|---------------|-----------------------------------------|------------------------------|

|                                                             | 6" (800x600) | 8" (1024x768) | 9" (1200x825)                           | Memory Storage Configuration |

| Main Display         Up to 5 pages         Up to 2 pages    |              |               | 1 page                                  | 4bpp packed                  |

| Full PIP Size         Up to 4 pages         Up to 1.3 pages |              | 0             | 1bpp, 2bpp and 4bpp packed (selectable) |                              |

| Cursor 4KB available 4KB available 4KB avail                |              | 4KB available | 1bpp, 2bpp and 4bpp packed (selectable) |                              |

| Max Framerate                                               | 85Hz         | 85Hz          | 50Hz                                    |                              |

### 2.5 Image Buffer Flexibility

- Host Writes can be rotated counter-clockwise by 90°, 180° or 270°

- New image data can be loaded to the image buffer while display updates are in progress

- Supported Data Formats: 1bpp, 2bpp, 4bpp and 1 byte-per-pixel

#### 2.6 Picture-In-Picture

- Picture in Picture support on separate buffer

- Independently Programmable Bit-Per-Pixel 1bpp, 2bpp and 4bpp

- Programmable Look-up-table availability for 1bpp and 2bpp for display bit-per-pixel matching

- Transparency key pixel value support.

- Background pixel inversion support.

## 2.7 Cursor Buffer Support

- Cursor buffer storage in internal memory.

- Dedicated 4K bytes of cursor buffer storage (in internal memory) independently programmable bit-per-pixel (1bpp, 2bpp or 4bpp)

- Extra memory for Multi-Buffered Cursor support.

- Transparency key pixel value support.

- Background pixel inversion support.

### 2.8 Thermal Sensor

• Power Management IC (PMIC) on-chip Thermal Sensor provides automatic temperature compensation.

# 2.9 Four Regulated Output Voltages for Source- and Gate-Driver Power Supplies

- Two source-driver power supplies can deliver up to 200mA.

- Positive source-driver power supply regulation voltage (VPOS) of +15V.

- Negative source-driver supply voltage (VNEG) tightly regulated to VPOS within ±50mV.

- Two gate-driver power supplies can deliver up to 20mA.

- +22V positive gate-driver power supply (GVDD) and -20V negative gate-driver power supply (GVEE).

## 2.10 VCOM Power Supply

- Negative output VCOM voltage programmable from -0.5V to -3.05V in 10mV steps.

- Non-volatile memory for storing programmed VCOM voltage, automatically loaded at power-up.

## 2.11 Controlled Inrush Current During Soft Start

• All outputs are brought up with soft-start control to limit the inrush current.

## 2.12 Clock Source

• No external clock source required.

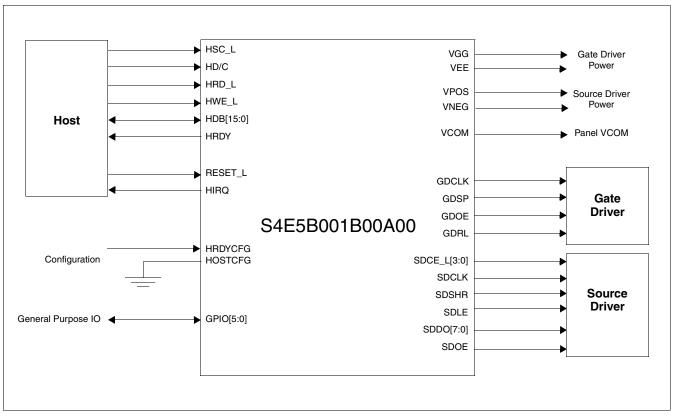

Figure 3-1: Typical 16-Bit Parallel Host Interface System Implementation

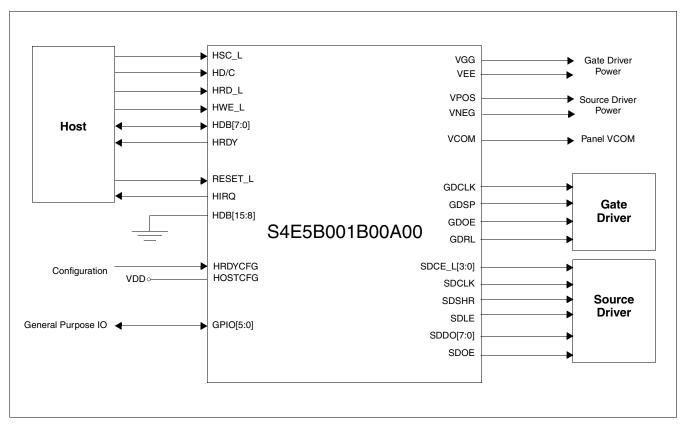

Figure 3-2: Typical 8-Bit Parallel Host Interface System Implementation

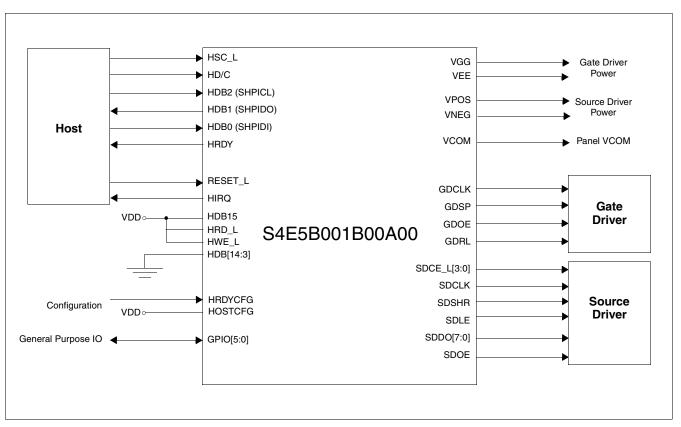

Figure 3-3: Typical Serial (SPI) Host Interface System Implementation

## **Chapter 4 Pins**

#### 4.1 Pinout Diagram

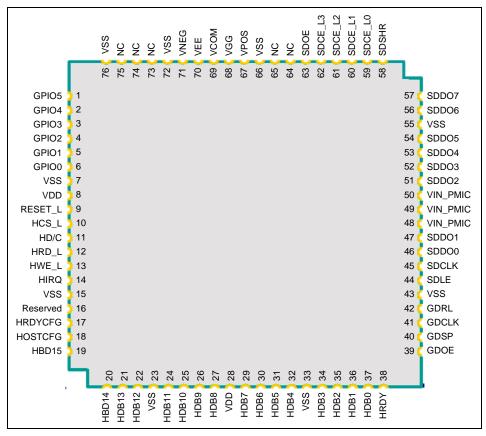

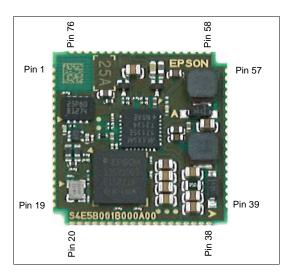

Figure 4-1: Pin Mapping (Top View)

Figure 4-2: Pin Position Identification

## 4.2 Pin Descriptions

#### Key:

| Pin Types |   |                               |

|-----------|---|-------------------------------|

| I         | = | Input                         |

| 0         | = | Output                        |

| IO        | = | Bi-Directional (Input/Output) |

| Р         | = | Power pin                     |

|           |   |                               |

#### **RESET# States**

| Н | = | High level output           |

|---|---|-----------------------------|

| L | = | Low level output            |

| Z | = | High Impedance (Hi-Z)       |

| 1 | = | Pull-up resistor on input   |

| 0 | = | Pull-down resistor on input |

#### Table 4-1: Cell Descriptions

| Item  | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| IC    | High voltage LVCMOS input buffer                                                                    |

| ICS   | High voltage LVCMOS Schmitt input buffer                                                            |

| ICD2  | High voltage LVCMOS input buffer with pull-down (100k $\Omega$ @3.3V)                               |

| 0     | High voltage low noise output buffer (4mA@3.3V)                                                     |

| O4    | High voltage low noise output buffer (12mA@3.3V)                                                    |

| ОН    | High voltage high speed output buffer (4mA@3.3V)                                                    |

| BC    | High voltage LVCMOS low noise bi-directional buffer (4mA@3.3V)                                      |

| BCS   | High voltage LVCMOS schmitt low noise bi-directional buffer (4mA@3.3V)                              |

| BCD2  | High voltage LVCMOS low noise bi-directional buffer (4mA@3.3V) with pull-down (100k $\Omega$ @3.3V) |

| ILTR  | Low voltage transparent input buffer                                                                |

| OLTR  | Low voltage transparent output buffer                                                               |

| ILTSD | Low voltage test mode control input buffer with pull-down                                           |

#### 4.2.1 Shared Host Interface

| Pin Name | Туре | Pin # | Cell | RESET_L<br>State | Description                                                                                                                                                                                                                                                |

|----------|------|-------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_L  | I    | 9     | ICS  | _                | This active low input sets all internal registers to their default<br>states and forces all signals to their inactive states. When<br>unused, this pin should be connected to VDD.<br>For RESET_L timing details, see 6.2, "RESET_L Timing" on<br>page 23. |

| HIRQ     | 0    | 14    | 0    | L                | This output pin is the Host IRQ.                                                                                                                                                                                                                           |

Table 4-2: Shared Host Interface Pin Descriptions

#### 4.2.2 Host Interface

These pins are used for the Host interface which can be selected from Intel 80 16-bit, Intel 80 8-bit, or Serial Host based on the setting of the HOSTCFG pin and HDB15.

| Pin Name  | Туре | Pin #                                                                      | Cell | RESET_L<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|------|----------------------------------------------------------------------------|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDB[15:0] | ю    | 19, 20, 21,<br>22, 24, 25,<br>26, 27, 29,<br>30, 31, 32,<br>34, 35, 36, 37 | BC   | Z                | <ul> <li>These input/output pins have multiple functions.</li> <li>For Intel 80 16-bit (HOSTCFG = 0), these pins are the shared command/parameter lines 15-0.</li> <li>For Intel 80 8-bit (HOSTCFG = 1 and HDB15 = 0), HDB[7:0] are the shared address/data lines 7-0. HDB[14:8] must be connected to VSS.</li> <li>For Serial Host (HOSTCFG = 1 and HDB15 = 1), HDB0 is the serial data input, SHPIDI. HDB1 is the serial data output, SHPIDO. HDB2 is the serial clock, SHPICK. HDB[14:3] must be connected to VSS.</li> </ul> |

| HWE_L     | I    | 13                                                                         | ICS  | _                | <ul> <li>This active low input pin has multiple functions.</li> <li>For Intel 80 16-bit (HOSTCFG = 0), this pin is the Write Enable signal.</li> <li>For Intel 80 8-bit (HOSTCFG = 1 and HDB15 = 0), this pin is the Write Enable signal.</li> <li>For Serial Host (HOSTCFG = 1 and HDB15 = 1), this pin must be connected to VDD.</li> </ul>                                                                                                                                                                                    |

| HRD_L     | 1    | 12                                                                         | ICS  | _                | <ul> <li>This active low input pin has multiple functions.</li> <li>For Intel 80 16-bit (HOSTCFG = 0), this pin is the Read Enable signal.</li> <li>For Intel 80 8-bit (HOSTCFG = 1 and HDB15 = 0), this pin is the Read Enable signal.</li> <li>For Serial Host (HOSTCFG = 1 and HDB15 = 1), this pin must be connected to VDD.</li> </ul>                                                                                                                                                                                      |

| HCS_L     | Ι    | 10                                                                         | IC   |                  | This active low input pin is the Chip Select signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 4-3: Host Interface Pin Descriptions

| Pin Name | Туре | Pin # | Cell | RESET_L<br>State | Description                                                                                                                 |

|----------|------|-------|------|------------------|-----------------------------------------------------------------------------------------------------------------------------|

| HD/C     | I    | 11    | IC   | _                | This input pin selects between Command (0) and Parameter (1).                                                               |

| HRDY     | Ю    | 38    | BC   | н                | This active high pin is the Host interface Ready (or WAIT)<br>signal.<br>When not used, this pin should be left unconnected |

Table 4-3: Host Interface Pin Descriptions (Continued)

#### 4.2.3 Gate Driver Interface

These pins are for the Gate Driver interface.

| Pin Name | Туре | Pin # | Cell | RESET_L<br>State | Description                                               |

|----------|------|-------|------|------------------|-----------------------------------------------------------|

| GDOE     | 0    | 39    | 0    | L                | This output pin is the output enable for the Gate Driver. |

| GDCLK    | 0    | 41    | 0    | L                | This output pin is the clock for the Gate Driver.         |

| GDSP     | 0    | 40    | 0    | Н                | This output pin is the Gate Driver Start Pulse.           |

| GDRL     | 0    | 42    | 0    | L                | This output pin is the Gate Driver Right or Left.         |

#### 4.2.4 Source Driver Interface

These pins are for the Source Driver interface.

Table 4-5: Source Driver Interface Pin Descriptions

| Pin Name    | Туре | Pin #                                | Cell | RESET_L<br>State | Description                                                 |

|-------------|------|--------------------------------------|------|------------------|-------------------------------------------------------------|

| SDCLK       | 0    | 45                                   | O4   | L                | This output pin is the clock for the Source Driver.         |

| SDLE        | 0    | 44                                   | O4   | L                | This output pin is the latch enable for the Source Driver.  |

| SDDO[7:0]   | 0    | 57, 56, 54,<br>53, 52, 51,<br>47, 46 | O4   | L                | These are the data output pins for the Source Driver.       |

| SDCE_L[3:0] | 0    | 62, 61, 60,<br>59                    | O4   | н                | These output pins are the Source Driver Chip Enables 3-0.   |

| SDSHR       | 0    | 58                                   | O4   | L                | This output pin is the Source Driver Shift Right Enable.    |

| SDOE        | 0    | 63                                   | O4   | L                | This output pin is the output enable for the Source Driver. |

#### 4.2.5 Miscellaneous

| Pin Name  | Туре | Pin #                 | Cell | RESET_L<br>State | Description                                                                                                                                                                                      |

|-----------|------|-----------------------|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HRDYCFG   | I    | 17                    | IC   | _                | This input pin is used for configuring the S4E5B001B00A00<br>and must be connected to either VDD or VSS. For a summary<br>of configuration options, see 4.3, "Configuration Pins" on page<br>20. |

| HOSTCFG   | I    | 18                    | IC   | _                | This input pin is used for configuring the S4E5B001B00A00<br>and must be connected to either VDD or VSS. For a summary<br>of configuration options, see 4.3, "Configuration Pins" on page<br>20. |

| GPIO[5:0] | Ю    | 1, 2, 3, 4, 5, 6      | BCD2 | Z                | These are the General Purpose Input/Output pins. When not used, these pins should be connected to VSS through a high value resistor (50k ~ 100k ohm).                                            |

| Reserved  | 10   | 16                    |      | —                | This reserved pin must be connected to VSS.                                                                                                                                                      |

| NC        | _    | 64, 65, 73,<br>74, 75 |      | —                | These pins must be left unconnected.                                                                                                                                                             |

Table 4-6: Miscellaneous Pin Descriptions

#### 4.2.6 Power and Ground

| Table 4-7: | Power | and Gro | und Pin | Descri | ptions |

|------------|-------|---------|---------|--------|--------|

|------------|-------|---------|---------|--------|--------|

| Pin Name | Туре | Pin#                                       | Cell | Power         | RESET_L<br>State | Description                           |

|----------|------|--------------------------------------------|------|---------------|------------------|---------------------------------------|

| VDD      | Р    | 8, 28                                      | Р    | +2.4V ~ +3.6V |                  | Module main power supply              |

| VIN_PMIC | Р    | 48, 49, 50                                 | Р    | +2.7V ~ +5.5V | _                | PMIC inverting regulator power supply |

| VSS      | Ρ    | 7, 15, 23,<br>33, 43,<br>55, 66,<br>72, 76 | Р    | οv            | _                | Ground                                |

| Pin Name | Туре | Pin# | Cell | Power          | RESET_L<br>State | Description                         |

|----------|------|------|------|----------------|------------------|-------------------------------------|

| VGG      | Р    | 68   | Р    | +22V           |                  | Gate-driver positive power supply   |

| VEE      | Р    | 70   | Р    | -20V           |                  | Gate-driver negative power supply   |

| VPOS     | Р    | 67   | Р    | +15V           | _                | Source-driver positive power supply |

| VNEG     | Р    | 71   | Р    | -15V           | _                | Source-driver negative power supply |

| VCOM     | Р    | 69   | Р    | -0.5V ~ -3.05V | _                | Panel VCOM power supply             |

## 4.3 Configuration Pins

The S4E5B001B00A00 has 3 configuration pins which should be pulled high or low based on the following table.

| CNF Pin | 1 (Connected to VDD)                              | 0 (Connected to VSS)             |

|---------|---------------------------------------------------|----------------------------------|

| HRDYCFG | HRDY only driven when HCS_L is asserted           | HRDY is always driven            |

| HOSTCFG | Intel 80 8-bit or Serial Host selected (see Note) | Intel 80 16-bit Host is selected |

Table 4-9: Configuration Pin Summary

#### Note

When HOSTCFG = 1, the HDB15 pin is used to select between the Intel 80 8-bit or Serial Host interfaces. For pin mapping details, see 4.4.1, "Host Interface Modes" on page 20.

### 4.4 Pin Mapping

#### 4.4.1 Host Interface Modes

The Host interface can be configured to either Intel 80 16-bit, Intel 80 8-bit, or Serial Host based on the setting of the HOSTCFG pin and HDB15. The following table summarizes the Host Interface configurations.

| Pin Name  | HOSTCFG = 0                       | HOSTCFG = 1, HDB15 = 0           | HOSTCFG = 1, HDB15 = 1                                                             |  |

|-----------|-----------------------------------|----------------------------------|------------------------------------------------------------------------------------|--|

| Fin Name  | 16-bit Host                       | 8-Bit Host                       | Serial Host                                                                        |  |

| HD/C      | 0 - Command<br>1 - Parameter      | 0 - Command<br>1 - Parameter     | 0 - Command<br>1 - Parameter                                                       |  |

| HDB[7:0]  | Shared<br>Command/Parameter[7:0]  | Shared<br>Command/Parameter[7:0] | HDB[0] - SHPIDI<br>HDB[1] - SHPIDO<br>HDB[2] - SHPICK<br>HDB[7:3] - Connect to VSS |  |

| HDB[15:8] | Shared<br>Command/Parameter[15:8] | Connect to VSS                   | HDB[15] -Connect to VDD<br>HDB[14:8] - Connect to VSS                              |  |

| HCS_L     | Cycle Enable                      | Cycle Enable                     | SHPICS_L                                                                           |  |

| HRD_L     | Read Enable                       | Read Enable                      | Connect to VDD                                                                     |  |

| HWE_L     | Write Enable                      | Write Enable                     | Connect to VDD                                                                     |  |

| HRDY      | Wait line                         | Wait line                        | Wait Line                                                                          |  |

Table 4-10: Host Interface Selection

The 8-bit parallel host interface can access commands and write to memory, but memory cannot be read back.

# Chapter 5 D.C. Characteristics

## 5.1 Absolute Maximum Ratings

Table 5-1: Absolute Maximum Ratings

| Symbol   | Parameter                               | Rating                 | Units |

|----------|-----------------------------------------|------------------------|-------|

| VDD      | Module Main Supply Voltage              | VSS - 0.3 ~ 4.0        | V     |

| VIN_PMIC | PMIC Inverting Regulator Supply Voltage | VSS - 0.3 ~ 6.0        | V     |

| VIN      | Input Signal Voltage                    | VSS - 0.3 ~ *VDD + 0.5 | V     |

| VOUT     | Output Signal Voltage                   | VSS - 0.3 ~ *VDD + 0.5 | V     |

| IOUT     | Output Signal Current                   | ±10                    | mA    |

| TSTG     | Storage Temperature                     | -55 ~ 150              | °C    |

#### Note

$V_{SS} = 0 V$

## 5.2 Recommended Operating Conditions

Table 5-2: Recommended Operating Conditions

| Symbol   | Parameter                                  | Condition | Min | Тур | Max | Units |

|----------|--------------------------------------------|-----------|-----|-----|-----|-------|

| VDD      | Module Main Supply Voltage                 | VSS = 0 V | 2.4 | 3.3 | 3.6 | V     |

| VIN_PMIC | PMIC Inverting Regulator Supply<br>Voltage | VSS = 0 V | 2.7 | 3.3 | 5.5 | V     |

| VIN      | Input Signal Voltage                       | —         | VSS | _   | VDD | V     |

| TOPR     | Operating Temperature                      | —         | -20 | 25  | 85  | °C    |

## **5.3 Electrical Characteristics**

| Symbol        | Parameter                       | Condition                             | Min   | Тур   | Max       | Units |

|---------------|---------------------------------|---------------------------------------|-------|-------|-----------|-------|

| ISLP_VIN_PMIC | Sleep mode current for VIN_PMIC | Sleep mode, no floating input for VDD | _     | 0.011 | _         | mA    |

| ISLP_VDD      | Sleep mode current for VDD      | Sleep mode, no floating input         | _     | 0.205 | _         | mA    |

| IIZ           | Input Leakage Current           | —                                     | -5    | —     | 5         | μΑ    |

| IOZ           | Output Leakage Current          | —                                     | -5    | —     | 5         | μΑ    |

| IOH           | High Level Output Current       | VDD = min<br>VOH = VDD - 0.4 V        | -4    | _     | _         | mA    |

| IOH4          | High Level Output Current       | VDD = min<br>VOH = VDD - 0.4 V        | -12   | _     | _         | mA    |

| IOL           | Low Level Output Current        | VDD = min<br>VOL = 0.4 V              | 4     | _     | _         | mA    |

| IOL4          | Low Level Output Current        | VDD = min<br>VOL = 0.4 V              | 12    | _     | _         | mA    |

| VIH           | High Level Input Voltage        | LVCMOS Level<br>VDD = max             | 2.2   | _     | VDD + 0.3 | V     |

| VIL           | Low Level Input Voltage         | LVCMOS Level<br>VDD = min             | -0.3  | _     | 0.8       | V     |

| VPOS          | VPOS Output Voltage             | —                                     | —     | 15    | —         | V     |

| VNEG          | VNEG Output Voltage             | —                                     | —     | -15   | —         | V     |

| VGG           | VGG Output Voltage              | —                                     | —     | 22    |           | V     |

| VEE           | VEE Output Voltage              | —                                     | —     | -20   |           | V     |

| VCOM          | VCOM Output Voltage             | —                                     | -3.05 | -1.77 | -0.5      | V     |

| IVPOS         | VPOS Output Current             | —                                     | —     | —     | 200       | mA    |

| IVNEG         | VNEG Output Current             | —                                     |       | —     | 200       | mA    |

| IVGG          | VGG Output Current              | —                                     | —     | —     | 20        | mA    |

| IVEE          | VEE Output Current              | —                                     | —     | —     | 20        | mA    |

| IVCOM         | VCOM Output Current             | —                                     | 70    | -     | —         | mA    |

| RPU           | Pull-Up Resistance              | VIN = 0 V                             | 50    | 100   | 240       | kΩ    |

| RPD           | Pull-Down Resistance            | VIN = VDD                             | 50    | 100   | 240       | kΩ    |

| CI            | Input Pin Capacitance           | f = 1MHz, VDD = 0V                    | —     | —     | 6         | pF    |

| СО            | Output Pin Capacitance          | f = 1MHz, VDD = 0V                    | —     | —     | 6         | pF    |

| CIO           | Bi-Directional Pin Capacitance  | f = 1MHz, VDD = 0V                    | —     | —     | 6         | pF    |

Table 5-3: Electrical Characteristics

# Chapter 6 A.C. Timings

### 6.1 Power-On Sequence

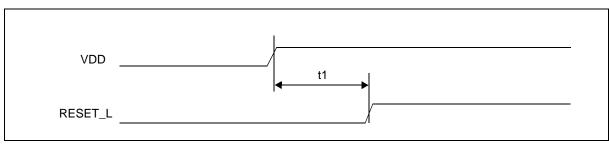

Figure 6-1: Power-On Sequence

Table 6-1: Power-On Sequence

| Symbol | Parameter                      | Min | Max | Units |

|--------|--------------------------------|-----|-----|-------|

| t1     | RESET_L deasserted from VDD on | 4   |     | ms    |

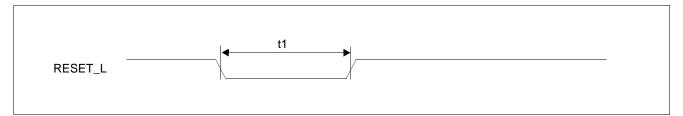

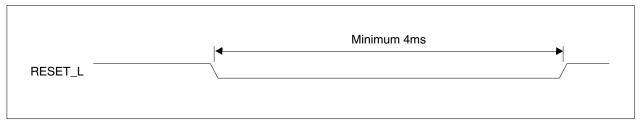

## 6.2 RESET\_L Timing

Figure 6-2: S4E5B001B00A00 RESET\_L Timing

| Symbol | Parameter                | Min | Max | Units |

|--------|--------------------------|-----|-----|-------|

| t1     | Active Reset Pulse Width | 4   |     | ms    |

## 6.3 Host Interface Timing

#### 6.3.1 Intel 80 Host Interface Timing

The following section provides AC timing information for the Intel 80 16-bit Host interface, which is selected when HOSTCFG = 0, and Intel 80 8-bit Host interface, which is selected when HOSTCFG = 1 and HDB15 = 0.

For a detailed description of the Host Interface pins, see Chapter 4.2.2, "Host Interface" on page 17.

Figure 6-3: Intel 80 Host Interface Write Timing

Figure 6-4: Intel 80 Host Interface Read Timing

| Signal    | Symbol                | Parameter                                                                                 | Min      | Мах                               | Units | Descriptio<br>n |

|-----------|-----------------------|-------------------------------------------------------------------------------------------|----------|-----------------------------------|-------|-----------------|

|           | t <sub>ast</sub>      | Address setup time (read/write)                                                           | 0        | —                                 | ns    |                 |

| HD/C      | t <sub>wah</sub>      | Address hold time (write)                                                                 | 3.7      | —                                 | ns    |                 |

|           | t <sub>rah</sub>      | Address hold time (read)                                                                  | 2.9      | _                                 | ns    |                 |

|           | t <sub>wcs</sub>      | Chip Select setup time to HWE_L falling edge                                              | 1.8      | _                                 | ns    |                 |

| HCS_L     | t <sub>rcs</sub>      | Chip Select setup time to HRD_L falling edge                                              | 2.2      | _                                 | ns    |                 |

|           | t <sub>ch</sub>       | Chip Select hold time (read/write)                                                        | 3.4      | _                                 | ns    |                 |

|           | t <sub>wl</sub>       | Pulse low duration                                                                        | (Note 1) | t <sub>wc</sub> - t <sub>wh</sub> | ns    |                 |

|           | t <sub>wh</sub>       | Pulse high duration                                                                       | (Note 1) | t <sub>wc</sub> - t <sub>wl</sub> | ns    |                 |

| HWE_L     |                       | Write cycle for Registers                                                                 | 76.9     | _                                 | ns    |                 |

|           | t <sub>wc</sub>       | Write cycle for Memory                                                                    | 76.9     |                                   | ns    |                 |

|           | t <sub>w2r</sub>      | HWE_L rising edge to HRD_L falling edge                                                   | 30.76    |                                   | ns    |                 |

|           | t <sub>r2w</sub>      | HRD_L rising edge to HWE_L falling edge                                                   | 0        | _                                 | ns    |                 |

|           |                       | Read cycle for Registers                                                                  | 76.9     |                                   | ns    |                 |

| ו ממוו    | t <sub>rc</sub>       | Read cycle for Memory                                                                     | 76.9     | _                                 | ns    |                 |

| HRD_L     |                       | Pulse low duration (for Registers)                                                        | 61.52    | t <sub>rc</sub> - t <sub>rh</sub> | ns    |                 |

|           | t <sub>rl</sub>       | Pulse low duration (for Memory)                                                           | (Note 1) | t <sub>rc</sub> - t <sub>rh</sub> | ns    |                 |

|           | t <sub>rh</sub>       | Pulse high duration                                                                       | (Note 1) | t <sub>rc</sub> - t <sub>rl</sub> | ns    |                 |

|           | t <sub>dst</sub>      | Write data setup time (16-bit bus)                                                        | 7.1      | _                                 | ns    |                 |

|           | t <sub>dst</sub>      | Write data setup time (8-bit bus)                                                         | 1.7      |                                   | ns    |                 |

|           | t <sub>dht</sub>      | Write data hold time (16-bit bus)                                                         | 4.8      | _                                 | ns    |                 |

|           | t <sub>dht</sub>      | Write data hold time (8-bit bus)                                                          | 4.7      | _                                 | ns    |                 |

|           | t <sub>rodh</sub>     | Read data hold time from HRD_L rising edge                                                | 3.2      |                                   | ns    |                 |

|           | t <sub>rrdz</sub>     | HRD_L rising edge to HDB[15:0] Hi-Z (16-bit bus)                                          | 3.6      | 9.5                               | ns    |                 |

| HDB[15:0] | t <sub>rrdz</sub>     | HRD_L rising edge to HDB[7:0] Hi-Z (8-bit bus)                                            | 3.9      | 9.6                               | ns    |                 |

|           | -                     | HRD_L falling edge to HDB[15:0]/HDB[7:0] valid for Registers                              | _        | 83.52                             | ns    |                 |

|           |                       | HRD_L falling edge to HDB[15:0]/HDB[7:0] valid for<br>Memory (if t <sub>rc</sub> not met) | _        | 83.42                             | ns    | – CL=30pF       |

|           | t <sub>rdd</sub>      | HRD_L falling edge to HDB[15:0] driven (16-bit bus)                                       | 4.4      | 17.0                              | ns    | CL=30pF         |

|           | t <sub>rdd</sub>      | HRD_L falling edge to HDB[7:0] driven (8-bit bus)                                         | 3.5      | 7.1                               | ns    | CL=30pF         |

|           | t <sub>rdyd</sub>     | HCS_L falling edge to HRDY driven (16-bit bus)                                            | 3.7      | 13.8                              | ns    | CL=30pF         |

|           | t <sub>rdyd</sub>     | HCS_L falling edge to HRDY driven (8-bit bus)                                             | 3.8      | 11.5                              | ns    | CL=30pF         |

|           | t <sub>rdyz</sub>     | HCS_L rising edge to HRDY Hi-Z (16-bit bus)                                               | 2.0      | 5.4                               | ns    | CL=30pF         |

|           | t <sub>rdyz</sub>     | HCS_L rising edge to HRDY Hi-Z (8-bit bus)                                                | 2.4      | 5.5                               | ns    | CL=30pF         |

|           | t <sub>rrdyl</sub>    | HRD_L falling edge to HRDY low                                                            | —        | 16.7                              | ns    | CL=30pF         |

| HRDY      | t <sub>rrdyh</sub>    | HRD_L falling edge to HRDY high                                                           | —        | 85.12                             | ns    | CL=30pF         |

|           | t <sub>rdyrw</sub>    | HRDY rising edge to HRD_L/HWE_L rising edge                                               | 146.4    | —                                 | ns    | CL=30pF         |

|           | tauratul              | HWE_L rising edge to HRDY falling edge (for command accesses)                             |          | 16.4                              | ns    | CL=30pF         |

|           | t <sub>rwrdyl</sub>   | HRD_L/HWE_L rising edge to HRDY falling edge (for memory accesses)                        | _        | 15.8                              | ns    | CL=30pF         |

|           | t <sub>rrdylmem</sub> | HRDY low period for memory read/write                                                     | —        | 61.52                             | ns    | CL=30pF         |

| <i>Table 6-3:</i> | Intel 80  | Host  | Interface | AC Timing |

|-------------------|-----------|-------|-----------|-----------|

| 1000000           | 111101 00 | 11000 | 1         | 110 10000 |

1. The pulse width high and pulse width low parameters have no required minimum duration. However, a pulse must occur for the cycle to take place and must adhere to the formula as defined by the maximum value.

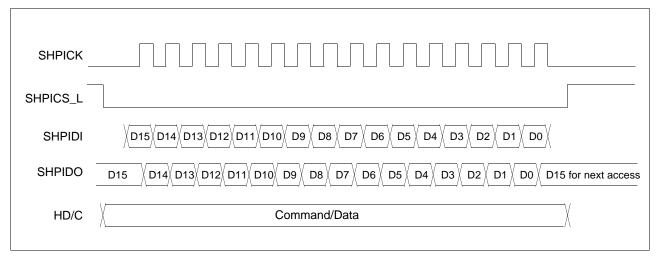

#### 6.3.2 Serial Host Interface Timing

The following section provides AC timing information for the Serial Host interface which is selected when HOSTCFG = 1 and HDB15 = 1.

For a detailed description of the Host Interface pins, see Chapter 4.2.2, "Host Interface" on page 17.

Figure 6-5: Serial Interface SHPICK Timing

| Symbol | Parameter                                  | Min | Max | Unit |

|--------|--------------------------------------------|-----|-----|------|

| t1     | SHPICS_L active to positive edge of SHPICK | 2   |     | ns   |

| t2     | SHPIDI setup to positive edge of SHPICK    | 9   |     | ns   |

| t3     | SHPIDI hold from positive edge of SHPICK   | 2   | —   | ns   |

| t4     | SHPICK period                              | 18  |     | ns   |

| t5     | Positive edge of SHPICK to SHPICS_L high   | 1   |     | ns   |

| t6     | Positive edge of SHPICK to SHPIDO hold     | 3   | 16  | ns   |

| t7     | HD/C setup to positive edge of SHPICK      | 3   | —   | ns   |

| t8     | HD/C hold from positive edge of SHPICK     | 1   | —   | ns   |

#### Table 6-4: Serial Interface SHPICK Timing

Figure 6-6: Serial Host Interface HRDY Timing

| Symbol | Parameter                                                                  | Min | Max   | Unit |

|--------|----------------------------------------------------------------------------|-----|-------|------|

| t11    | Positive edge of the 15th SHPICK to HRDY falling edge (for memory read)    | _   | 16    | ns   |

| t12    | HRDY low period for memory read/write                                      | _   | 61.52 | ns   |

| t13    | Positive edge of the 16th SHPICK to HRDY falling edge (for command access) | —   | 16    | ns   |

| t14    | Positive edge of the 16th SHPICK to HRDY falling edge (for memory write)   |     | 16    | ns   |

| Table 6-5: Serial | Interface HRDY | Timing |

|-------------------|----------------|--------|

|-------------------|----------------|--------|

# **Chapter 7 Power Management**

## 7.1 Power Management State Description

The S4E5B001B00A00 controller has the following power states:

• OFF State:

Power for the S4E5B001B00A00 and internal Memory is off. Upon power-up, the Host must issue a hardware reset and an INIT\_SYS\_RUN command to initialize the S4E5B001B00A00.

- Run State: The S4E5B001B00A00 is ready for operation. In this state the display can be updated.

- Standby State: The S4E5B001B00A00 is in power save mode. The Host should not access memory while in this state.

- Sleep Mode:

The S4E5B001B00A00 is in power save mode. Sleep Mode initiates the Power Pin power down cycles. The Host should not access memory while in this state.

The following table summarizes the S4E5B001B00A00 functionality for each power state.

| Power<br>Mode | S4E5B001B00A00Controller<br>State                                | S4E5B001B00A00<br>PLL State | PMIC State | Memory Data<br>Retained | Power<br>Consumption                                       |

|---------------|------------------------------------------------------------------|-----------------------------|------------|-------------------------|------------------------------------------------------------|

| OFF           | Unknown                                                          | Unknown                     | Unknown    | No                      | NA                                                         |

| Run           | Active<br>All clocks active                                      | Active                      | ON         | Yes                     | Low or High<br>(depending on host<br>and display activity) |

| Standby       | Power Save Mode<br>All module clocks gated off<br>PLL is running | Active                      | ON         | Yes                     | Lower                                                      |

| Sleep         | Power Save Mode<br>Power Pin cycle off<br>PLL off                | Powered-Down                | OFF        | Yes                     | Lowest                                                     |

Table 7-1: S4E5B001B00A00 Power State Functionality Summary

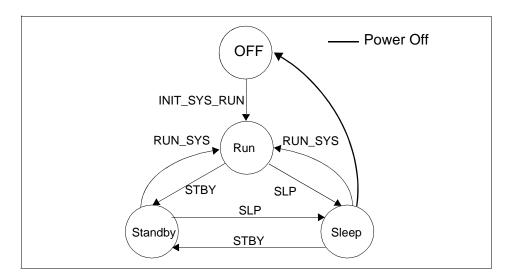

The following figure shows how to transition between S4E5B001B00A00 power states.

Figure 7-1: State Transition Diagram

To transition between S4E5B001B00A00 power states the following steps are required.

| Current | Next State Requirements                                           |                                                 |                 |                    |  |

|---------|-------------------------------------------------------------------|-------------------------------------------------|-----------------|--------------------|--|

| State   | Off                                                               | Run                                             | Standby         | Sleep              |  |

| OFF     | NA                                                                | 1. Power on Reset<br>2. Run Cmd<br>INIT_SYS_RUN | Not Possible.   | Not Possible.      |  |

| Run     | 1. Host Save Memory<br>Contents<br>2. Run Cmd SLP<br>3. Power off | NA                                              | 1. Run Cmd STBY | 1. Run Cmd SLP     |  |

| Standby | 1. Run Cmd SLP<br>2. Power off                                    | 1. Run Cmd RUN_SYS                              | NA              | 1. Run Cmd RUN_SYS |  |

| Sleep   | 1. Power off                                                      | 1. Run Cmd RUN_SYS                              | 1. Run Cmd STBY | NA                 |  |

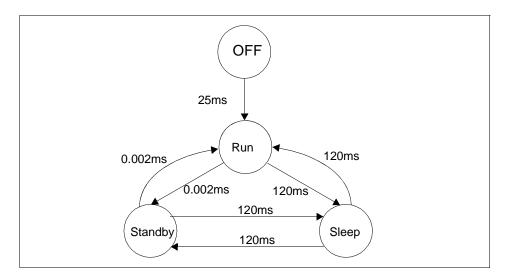

The estimated time required to transition between S4E5B001B00A00 power states is shown in the following figure and summarized in the following table.

Figure 7-2: State Transition Estimated Time

| Table 7-3. | State Transition | Estimated | Time    |

|------------|------------------|-----------|---------|

| 1000 / 5.  | Sidic Transmon   | Loundica  | 1 11110 |

| Current | Estimated Transition Time |         |         |       |

|---------|---------------------------|---------|---------|-------|

| State   | Off                       | Run     | Standby | Sleep |

| OFF     | NA                        | 25ms    | NA      | NA    |

| Run     | NA                        | NA      | 0.002ms | 120ms |

| Standby | NA                        | 0.002ms | NA      | 120ms |

| Sleep   | NA                        | 120ms   | 120ms   | NA    |

# Chapter 8 Host Interface

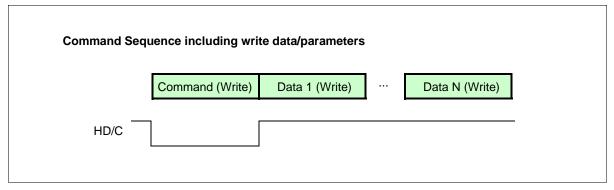

#### 8.1 Host Cycle Sequences

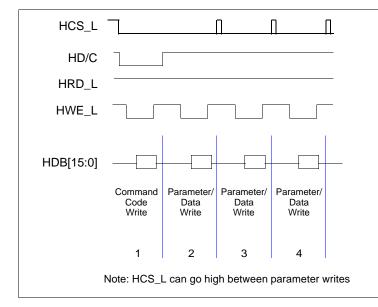

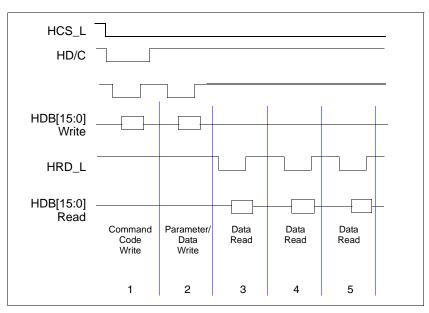

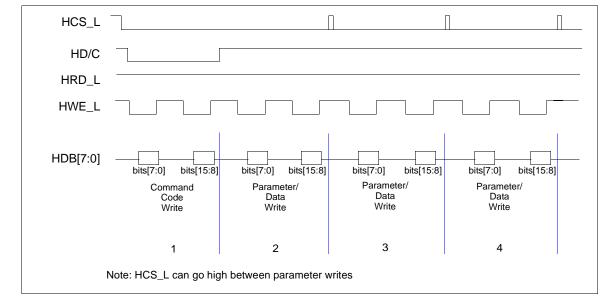

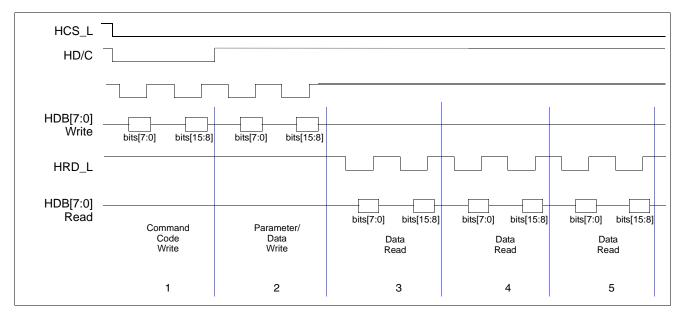

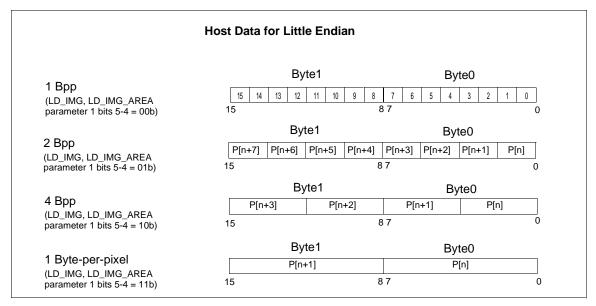

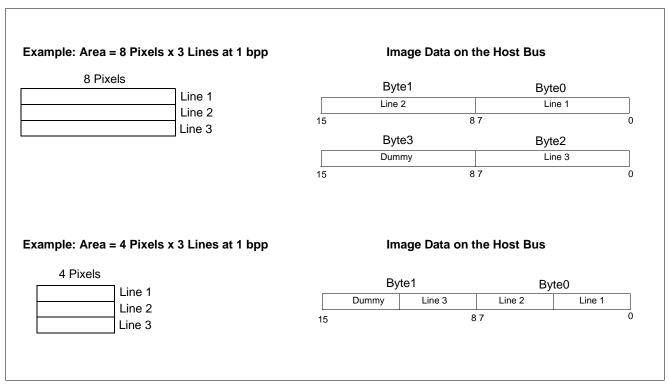

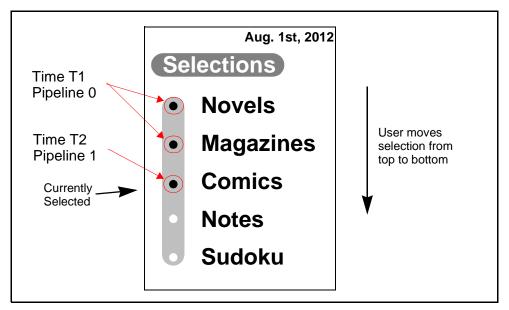

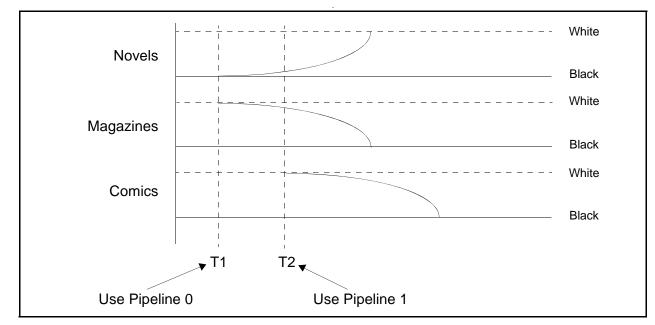

#### 8.1.1 Command and Parameter Cycle